- Highpoint Scsi & Raid Devices Driver Download Windows 10

- Highpoint SCSI & RAID Devices Driver Download

Controller Register Map¶

For RR44xx Intel IOP based adapters, the controller IOP is accessed via PCI BAR0 and BAR2

Downloads 37 Drivers, Manual and BIOS for HighPoint Rocket RAID 2640X1 HD Controller & Removable drive. Here's where you can download the newest software for your Rocket RAID 2640X1.

| BAR0 offset | Register |

|---|---|

| 0x11C5C | Link Interface IRQ Set |

| 0x11C60 | Link Interface IRQ Clear |

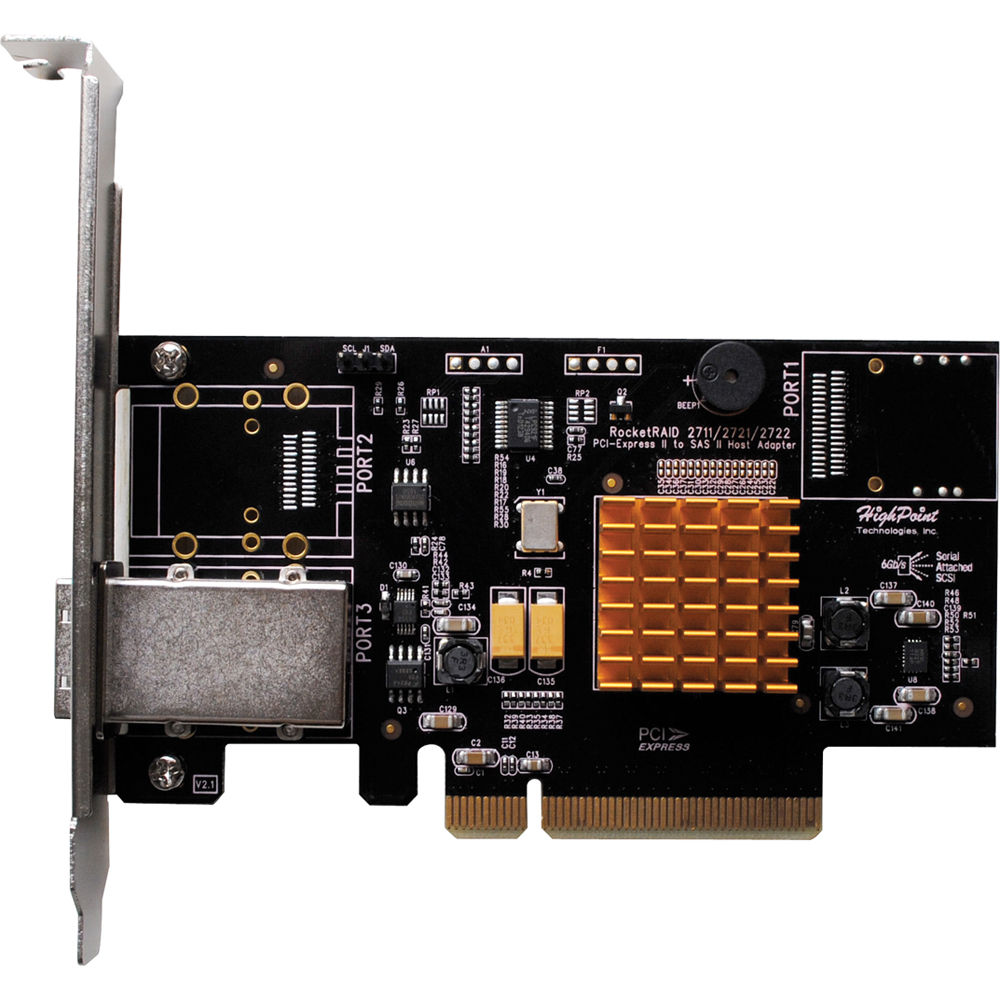

A product list of HighPoint SCSI And RAID for driver update, firmware upgrade and utility download. THUNDERBOLT 2 H/W RAID ADAPTER SUPPORTS 2X ESATA/ MINI-SAS UNITS Highpoint Rocketraid 2710 Sas Raid Controller - Serial Attached Scsi, Serial Ata/600 - Pci Express 2.0 X8 - Plug-in Card 0, 1, 5, 10, 50, Jbod Raid Level (rocketraid2710) 4CHANNEL 3G SATA PCIE RAID HBA 4X ESATA PORTS 3G VALUE RAID HBA 2X5G USB3/2X 6G ESATA PCIE HBA 2X 5G USB3PORTS/2X 6G ESATA PORTS HighPoint ROCKETRAID 2720SGL.

| BAR2 offset | Register |

|---|---|

| 0x10 | Inbound Message Register 0 |

| 0x14 | Inbound Message Register 1 |

| 0x18 | Outbound Message Register 0 |

| 0x1C | Outbound Message Register 1 |

| 0x20 | Inbound Doorbell Register |

| 0x24 | Inbound Interrupt Status Register |

| 0x28 | Inbound Interrupt Mask Register |

| 0x30 | Outbound Interrupt Status Register |

| 0x34 | Outbound Interrupt Mask Register |

| 0x40 | Inbound Queue Port |

| 0x44 | Outbound Queue Port |

For Intel IOP based adapters, the controller IOP is accessed via PCI BAR0:

| BAR0 offset | Register |

|---|---|

| 0x10 | Inbound Message Register 0 |

| 0x14 | Inbound Message Register 1 |

| 0x18 | Outbound Message Register 0 |

| 0x1C | Outbound Message Register 1 |

| 0x20 | Inbound Doorbell Register |

| 0x24 | Inbound Interrupt Status Register |

| 0x28 | Inbound Interrupt Mask Register |

| 0x30 | Outbound Interrupt Status Register |

| 0x34 | Outbound Interrupt Mask Register |

| 0x40 | Inbound Queue Port |

| 0x44 | Outbound Queue Port |

For Marvell not Frey IOP based adapters, the IOP is accessed via PCI BAR0 and BAR1:

| BAR0 offset | Register |

|---|---|

| 0x20400 | Inbound Doorbell Register |

| 0x20404 | Inbound Interrupt Mask Register |

| 0x20408 | Outbound Doorbell Register |

| 0x2040C | Outbound Interrupt Mask Register |

| BAR1 offset | Register |

|---|---|

| 0x0 | Inbound Queue Head Pointer |

| 0x4 | Inbound Queue Tail Pointer |

| 0x8 | Outbound Queue Head Pointer |

| 0xC | Outbound Queue Tail Pointer |

| 0x10 | Inbound Message Register |

| 0x14 | Outbound Message Register |

| 0x40-0x1040 | Inbound Queue |

| 0x1040-0x2040 | Outbound Queue |

For Marvell Frey IOP based adapters, the IOP is accessed via PCI BAR0 and BAR1:

| BAR0 offset | Register |

|---|---|

| 0x0 | IOP configuration information. |

| BAR1 offset | Register |

|---|---|

| 0x4000 | Inbound List Base Address Low |

| 0x4004 | Inbound List Base Address High |

| 0x4018 | Inbound List Write Pointer |

| 0x402C | Inbound List Configuration and Control |

| 0x4050 | Outbound List Base Address Low |

| 0x4054 | Outbound List Base Address High |

| 0x4058 | Outbound List Copy Pointer Shadow Base Address Low |

| 0x405C | Outbound List Copy Pointer Shadow Base Address High |

| 0x4088 | Outbound List Interrupt Cause |

| 0x408C | Outbound List Interrupt Enable |

| 0x1020C | PCIe Function 0 Interrupt Enable |

| 0x10400 | PCIe Function 0 to CPU Message A |

| 0x10420 | CPU to PCIe Function 0 Message A |

| 0x10480 | CPU to PCIe Function 0 Doorbell |

| 0x10484 | CPU to PCIe Function 0 Doorbell Enable |

I/O Request Workflow of Not Marvell Frey¶

All queued requests are handled via inbound/outbound queue port.A request packet can be allocated in either IOP or host memory.

To send a request to the controller:

Get a free request packet by reading the inbound queue port orallocate a free request in host DMA coherent memory.

The value returned from the inbound queue port is an offsetrelative to the IOP BAR0.

Requests allocated in host memory must be aligned on 32-bytes boundary.

Fill the packet.

Post the packet to IOP by writing it to inbound queue. For requestsallocated in IOP memory, write the offset to inbound queue port. Forrequests allocated in host memory, write (0x80000000|(bus_addr>>5))to the inbound queue port.

The IOP process the request. When the request is completed, itwill be put into outbound queue. An outbound interrupt will begenerated.

For requests allocated in IOP memory, the request offset is posted tooutbound queue.

For requests allocated in host memory, (0x80000000|(bus_addr>>5))is posted to the outbound queue. If IOP_REQUEST_FLAG_OUTPUT_CONTEXTflag is set in the request, the low 32-bit context value will beposted instead.

The host read the outbound queue and complete the request.

For requests allocated in IOP memory, the host driver free the requestby writing it to the outbound queue.

Non-queued requests (reset/flush etc) can be sent via inbound messageregister 0. An outbound message with the same value indicates the completionof an inbound message.

Highpoint Scsi & Raid Devices Driver Download Windows 10

I/O Request Workflow of Marvell Frey¶

All queued requests are handled via inbound/outbound list.

To send a request to the controller:

Allocate a free request in host DMA coherent memory.

Requests allocated in host memory must be aligned on 32-bytes boundary.

Fill the request with index of the request in the flag.

Fill a free inbound list unit with the physical address and the size ofthe request.

Set up the inbound list write pointer with the index of previous unit,round to 0 if the index reaches the supported count of requests.

Post the inbound list writer pointer to IOP.

The IOP process the request. When the request is completed, the flag ofthe request with or-ed IOPMU_QUEUE_MASK_HOST_BITS will be put into afree outbound list unit and the index of the outbound list unit will beput into the copy pointer shadow register. An outbound interrupt will begenerated.

The host read the outbound list copy pointer shadow register and comparewith previous saved read pointer N. If they are different, the host willread the (N+1)th outbound list unit.

The host get the index of the request from the (N+1)th outbound listunit and complete the request.

Non-queued requests (reset communication/reset/flush etc) can be sent via PCIeFunction 0 to CPU Message A register. The CPU to PCIe Function 0 Message registerwith the same value indicates the completion of message.

User-level Interface¶

Highpoint SCSI & RAID Devices Driver Download

The driver exposes following sysfs attributes:

| NAME | R/W | Description |

|---|---|---|

| driver-version | R | driver version string |

| firmware-version | R | firmware version string |

Copyright © 2006-2012 HighPoint Technologies, Inc. All Rights Reserved.

This file is distributed in the hope that it will be useful,but WITHOUT ANY WARRANTY; without even the implied warranty ofMERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See theGNU General Public License for more details.

The Highpointers Club doesn’t have a definitive online guide. There are plenty of books available at the Highpointers Merc including guidebooks by HPC members: Holmes, Wingers, and Zumwalt. Sources with current information are two interactive sites: summitpost.org and wikipedia.org. Summitpost is the definitive choice among climbers, although wikipedia has some amazing information on the mountains. The Highpointers Club maintains that the USGS Elevations and Distances is the official source for the Club. More details about adjustments to this list are described in “State Highpoints Recognized by the Club“.

David Kelly has produced two ARCSOFT interactive topo maps: State Highpoints and County Highpoints.

Please contact us at guides@highpointers.org if you have any suggestions for enhancing this guide.